# INTERNAL REPORTS IN

# SIMULATION, OPTIMIZATION AND CONTROL

No. SOC-185

YIELD OPTIMIZATION FOR ARBITRARY STATISTICAL DISTRIBUTIONS

PART II: IMPLEMENTATION

H.L. Abdel-Malek and J.W. Bandler

November 1977

(Revised June 1978, March 1979)

FACULTY OF ENGINEERING

McMASTER UNIVERSITY

HAMILTON, ONTARIO, CANADA

#### YIELD OPTIMIZATION FOR ARBITRARY STATISTICAL DISTRIBUTIONS

#### PART II: IMPLEMENTATION

H.L. Abdel-Malek, Member, IEEE, and J.W. Bandler, Fellow, IEEE

Abstract A suggested test problem for proposed algorithms in yield optimization is described in detail. The problem is a current switch emitter follower (CSEF) circuit originally described by Ho, which includes a transmission line. The ideas presented in Part I of this paper [1] are applied to this circuit in order to obtain an optimal statistical design. Production yield is maximized taking into consideration statistical distributions of circuit parameters and realistic correlations between transistor model parameters. Nonlinear programming employing the analytical formulas for yield and its sensitivities is used to provide optimal nominal values for the circuit parameters. Different design specifications are assumed and corresponding optimal designs are obtained.

This work was supported by the Natural Sciences and Engineering Research Council of Canada under grant A7239 and by a Postdoctoral Fellowship to H.L. Abdel-Malek. This paper was presented at the 1978 IEEE International Symposium on Circuits and Systems, New York, NY, May 17-19, 1978.

J.W. Bandler is with the Group on Simulation, Optimization and Control and Department of Electrical Engineering, McMaster University, Hamilton, Canada, L8S 4L7.

H.L. Abdel-Malek was with the Group on Simulation, Optimization and Control and Department of Electrical Engineering, McMaster University, Hamilton, Canada L8S 4L7. He is now with the Department of Engineering Physics and Mathematics, Faculty of Engineering, Cairo University, Giza, Egypt.

#### I. INTRODUCTION

Need is growing for test problems in the area of yield optimization. Several test problems, such as the Karafin filter [2-5], the LC lowpass filter [6,7] and the two-section transmission-line transformer [6,8], have been used by researchers both for demonstrating and for comparing proposed algorithms for tolerance assignment, design centering, yield analysis and optimization techniques. However, no such problem has been developed in the available literature in sufficient detail for comparing proposed techniques which take explicitly into account statistical distributions and possible correlations in providing an optimal design center.

Yield optimization has been considered by Elias [9] and by Becker and Jensen [10] using the Monte Carlo method of yield analysis. It was also considered by Bandler and Abdel-Malek [8] using linear cuts but for uniform distribution of outcomes between tolerance extremes. It has been recently considered indirectly by Brayton, Hachtel and Director [11] using the simplicial approximation.

A current switch emitter follower circuit which was previously investigated by Ho [12] in the context of sensitivity calculations is chosen for implementing the ideas presented in Part I [1] of this paper. A detailed description of the circuit is given in Section II. Felt to be a worthwhile preliminary exercise to statistical design, an optimal worst-case design is carried out in Section III [8]. Sparsity is exploited in developing the quadratic models for the constraints.

Correlations between transistor model parameters through formulas based on work published by Balaban and Golembeski [13] are established

in Section IV. According to these correlations, weights to be assigned to the orthocells are computed (see Part I of this paper). Production yield is maximized employing analytical formulas for yield and its sensitivities as well as the quadratic approximations to the design constraints. It is shown how different design specifications can be investigated and corresponding optimal yields obtained without any additional circuit simulations.

An appendix (to aid future work by other researchers) describing the derivation of the state equations used in analyzing the CSEF circuit is provided.

#### II. ANALYSIS OF THE CSEF

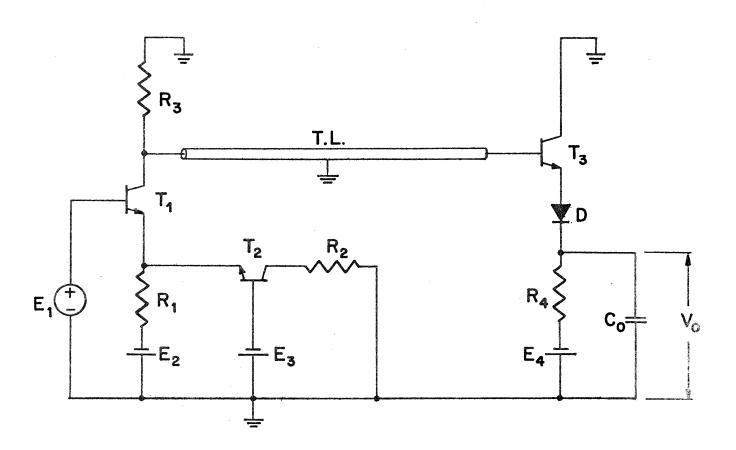

The circuit is shown in Fig. 1. The decoupled equivalent circuit of the transmission line is used [14]. Considering a lossless transmission line and the charge-control model of the transistors as well as the diode the circuit is shown in Fig. 2. The following two equations are used for the transmission-line model.

$$\begin{split} &u_{\mathbf{i}}(t) = \left[ \mathbf{e}_{0}(t-\tau) + Z_{0} \; \mathbf{i}_{0}(t-\tau) \right] \; \mathbf{U}(t-\tau) + \Phi_{\mathbf{i}}(t), \\ &u_{\mathbf{r}}(t) = \left[ \mathbf{e}_{\ell}(t-\tau) + Z_{0} \; \mathbf{i}_{\ell}(t-\tau) \right] \; \mathbf{U}(t-\tau) + \Phi_{\mathbf{r}}(t), \end{split}$$

where  $Z_0$  and  $\tau$  are the characteristic impedance and the delay time of the transmission line, respectively, U is the step function given by

$$U(t-\tau) = \left\{ \begin{array}{ccc} 0 & & t < \tau & , \\ & & \\ 1 & & t \ge \tau & . \end{array} \right.$$

The parameter  $\Phi$  represents the initial voltage distribution stored on the transmission line. Thus, we take

$$\Phi_{i}(t) = \Phi_{r}(t) = 0$$

for  $t \ge \tau$ .

The original circuit parameters and model parameters are given in Table

I. The state equations are formulated as described in the Appendix.

The subroutine CSEF [15] solves for the equilibrium, steady state solution which supplies initial values of the states in the subsequent integration. The subroutine DVOGER [16], based on Gear's integration algorithm [17], called from CSEF, is used for solving the state equations. The algorithm has a variable step and hence interpolation was used to find the values of  $u_i(t)$  and  $u_r(t)$  if  $t-\tau$  falls between time steps. Alternatively,  $\tau/n$ , where n is an integer can be used as a fixed step, however, integration will be expensive. Our analysis has been verified independently by the companion network approach [18].

#### III. WORST-CASE DESIGN OF THE CSEF

The parameter vector considered for a worst-case design (see Fig. 2) is

$$\phi = \begin{bmatrix} E_{4} \\ Z_{0} \\ R_{4} \\ C_{0} \end{bmatrix}.$$

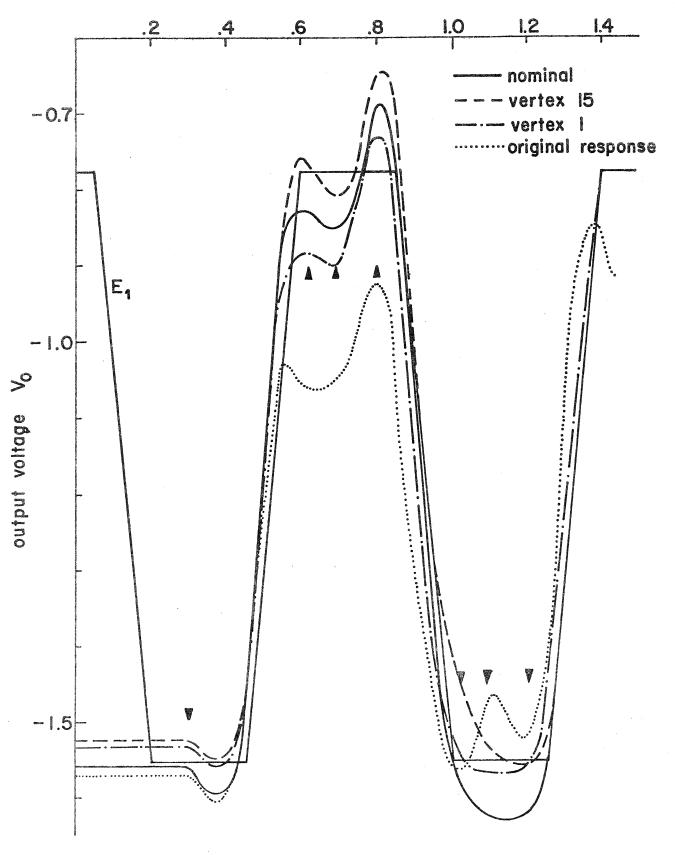

The corresponding tolerances are denoted by  $\epsilon_1$ ,  $\epsilon_2$ ,  $\epsilon_3$  and  $\epsilon_4$ . Fig. 3 shows the input voltage  $E_1$  and the time point constraints used. The response obtained with the parameter values in Table I are also shown.

The circuit is initially at equilibrium with  $E_1$  = -0.776 V.

Starting at the nominal parameter values given in Table I, the approximation to the design constraints was carried out by solving the system of equations (36) of Part I using the program MODEL4 [19]. The base points were obtained by equation (30) of Part I with

$$\frac{1.7}{0.0} = \begin{bmatrix} 1.7 \\ 50.0 \\ 50.0 \\ 1.5 \end{bmatrix}, \qquad \delta = \begin{bmatrix} 0.17 \\ 5.00 \\ 5.00 \\ 0.15 \end{bmatrix}$$

and

$$B = \begin{bmatrix} -0.2 & 0.6 & 0.5 & 0 & 0 & 0 \\ -0.3 & 0 & 0 & -1.0 & -0.5 & 0 \\ 0 & -0.5 & 0 & 1.0 & 0 & 0.2 \\ 0 & 0 & 0.5 & 0 & 0.4 & 0.4 \end{bmatrix}.$$

The values of the constraints  $g_i$  are obtained from the circuit response and the specifications shown in Fig. 3 using the program CSEF [15]. Each constraint  $g_i$  is described by a quadratic polynomial  $P_i$  having 15 coefficients.

The nonlinear program formulated to solve the worst-case design problem [8] is

minimize

$$E_{\mu}^{0}/\epsilon_{1} + Z_{0}^{0}/\epsilon_{2} + R_{\mu}^{0}/\epsilon_{3} + C_{0}^{0}/\epsilon_{\mu}$$

$\phi^{0}$ ,  $\epsilon$

subject to

$$P_{i}(\phi^{r}) \geq 0, r = 1, 2, ..., 2^{4},$$

$i = 1, 2, ..., 7,$

where  $\phi^{\mathbf{r}}$  indicates a vertex of the tolerance orthotope as given by

equation (8) of Part I. The output capacitor  $C_0$  was constrained such that

$$C_0^0 - \epsilon_{4} \ge 1.0 \text{ pF}.$$

This constraint was designed to prevent an unrealistic nominal value.

This nonlinear program was transformed into a minimax problem using the Bandler-Charalambous technique [20]. The program FLOPT4 [21] was used to solve the resulting minimax problem and the program QPE [19] was used for calculating the quadratic polynomials at the vertices. The optimum nominal point obtained was far from the center of interpolation  $\overline{\phi}$ . In order to have a reliable approximation, the time point constraints were reapproximated around the obtained nominal  $\phi$ , i.e., the new center of interpolation is

$$\frac{1.70}{0.00} = 0.00$$

$$\frac{1.70}{0.00}$$

$$\frac{1.35}{0.00}$$

Again, the base points were obtained by equation (30) of Part I using the same B matrix given before and with

$$\delta = \begin{bmatrix} 0.17 \\ 14.25 \\ 9.0 \\ 0.3375 \end{bmatrix}.$$

The nonlinear program was solved employing the updated approximations. The optimal worst-case nominal parameters and

tolerances are shown in Table II. The nominal design response as well as the responses for the critical vertices, numbered according to equation (9) of Part I, are shown in Fig. 3.

A single interpolation region was found to be satisfactory. The difference between the predicted responses at vertices according to the approximations and the actual responses subsequently checked by integration was, over the sample points used, less than 2%.

For the worst-case design obtained the power dissipated in the output circuit is 0.1854 mW at the nominal solution. It is 0.365 mW for the original design at equilibrium when  $\rm E_1$  = -0.776. This saves power and limits fluctuations in chip temperature.

#### IV. STATISTICAL DESIGN OF THE CSEF

The output section of the CSEF circuit was optimally designed to provide maximum yield. The statistical distributions of the circuit parameters and the transistor model parameters were assumed to be fixed. The nominal values of the output circuit parameters were optimized in order to obtain maximum yield.

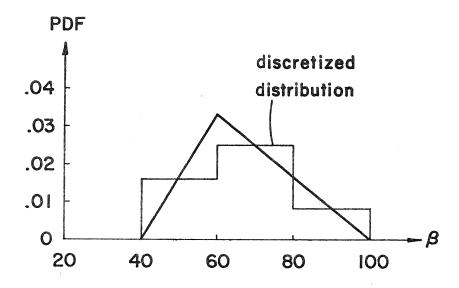

The statistical distributions of the transistor  $T_3$  model parameters are based upon results published by Butler [22] and by Balaban and Golembeski [13]. The transistor current gain  $\beta$  was assumed to have a triangular probability distribution function with a peak at  $\beta$  = 60 and 40  $\leq \beta \leq$  100, as illustrated in Fig. 4. Correlation between transistor model parameters (see Table I(c)) was established according to the following equations

$$I_S = 0.0061 \text{ } \beta \text{ } (1 + 0.3516 \text{ } X_{r1}) \text{ } \times 10^{-9} \text{ } A \text{ } ,$$

$$C_{JE} = (0.144 - 0.242 \times 10^{-3} \beta) \text{ } (1 + 0.2 \text{ } X_{r2}) \text{ } pF \text{ } ,$$

$$TT = 0.01 \text{ } (1 + 0.2 \text{ } X_{r3}) \text{ } ns,$$

where  $\mathbf{X}_{ri}$  are independent uniformly distributed random numbers over the range

$$-1 \le X_{ri} \le 1$$

, i = 1, 2, 3.

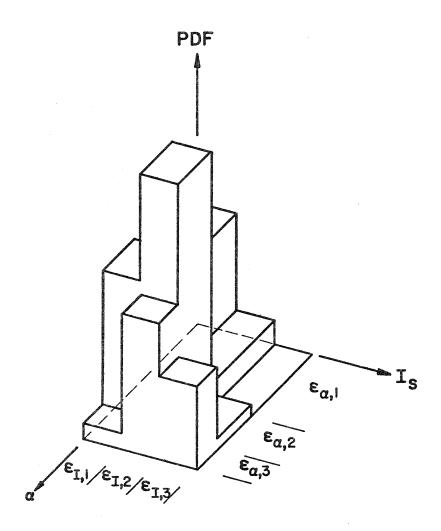

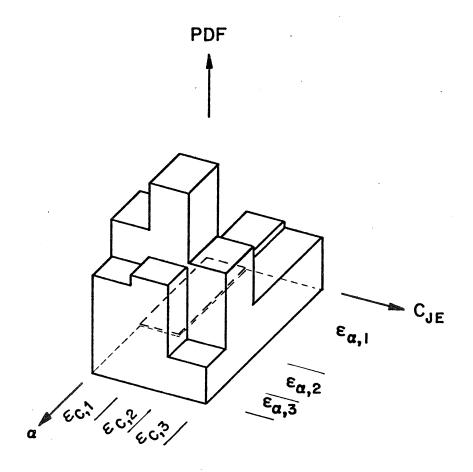

The discretized joint probability density functions of the common base current gain  $\alpha$  =  $\beta/(\beta+1)$  and  $I_S$  and that of  $\alpha$  and  $C_{JE}$  are shown in Fig. 5 and Fig. 6, respectively. The numerical coefficients in each of these equations were obtained by preserving the ratios of the corresponding coefficients of Balaban and Golembeski [13] and, at the same time, ensuring that they lead to the same nominal values we have. According to these distributions the weights and intervals for the discretized distribution were determined and are shown in Table III. As a matter of fact the weights should be available from the sampled data used in formulating these equations.

The circuit parameters were assumed to have the distributions

$$E_{\mu} = E_{\mu}^{0} + 0.1632 X_{r\mu} ,$$

$$Z_{0} = Z_{0}^{0} + 9.5 X_{r5} ,$$

$$R_{\mu} = R_{\mu}^{0} + 4.4 X_{r6} ,$$

$$C_{0} = C_{0}^{0} + 0.27 X_{r7} ,$$

where, again,

$$-1 \le X_{ri} \le 1$$

, i = 4, 5, 6, 7.

The nonlinear programming problem to be solved is

subject to

$$C_0^0 \ge 1.27 \text{ pF},$$

$$z_0^0 \le z_{0u}$$

,

where  $\boldsymbol{z}_{0u}$  is an upper bound on the characteristic impedance of the transmission line and

The production yield Y is calculated using equations (61) and (53) of Part I. The linear cuts are obtained from the quadratic approximations to the design constraints

$$V_0(t) \le -1.45 \text{ V}, t = 0.3 \text{ ns},$$

$$V_0(t) \ge -0.85 \text{ V}, t = 0.62, 0.69, 0.8 \text{ ns},$$

$$V_0(t) \le -1.40 \text{ V}, t = 1,02, 1.09, 1.2 \text{ ns},$$

using equation (42) of Part I, where

$$\phi^{a} = \begin{bmatrix} \phi^{0} \\ \alpha_{3} \\ I_{S3} \\ C_{JE3} \\ TT_{3} \end{bmatrix}$$

The value of  $\phi^0$  is varying as determined during the optimization process while the remaining parameters have the fixed values given in Table IV.

A single quadratic approximation to the design constraints was carried out at the interpolation region defined by the center and size shown in Table IV. The base points are obtained from equation (30) of Part I, where B is given by equation (31) of Part I and where

$$u_{5} = \begin{bmatrix} 0.2 \\ 0.3 \\ 0.6 \\ -0.7 \\ 0.8 \end{bmatrix}, \quad T_{5} = \begin{bmatrix} 0.4 \\ -0.5 \\ -0.7 \\ 0.6 \end{bmatrix},$$

$$u_{4} = \begin{bmatrix} 0.2 \\ -0.6 \\ 0.5 \\ 0.8 \end{bmatrix}, \quad T_{4} = \begin{bmatrix} 0.6 \\ 0.7 \\ -0.6 \\ 0.3 \end{bmatrix},$$

$$u_{3} = \begin{bmatrix} 1.0 \\ -1.0 \\ 1.0 \end{bmatrix}, \quad T_{3} = \begin{bmatrix} -0.8 \\ -1.0 \\ -0.9 \end{bmatrix},$$

$$u_{2} = \begin{bmatrix} 1.0 \\ -0.9 \end{bmatrix}, \quad T_{2} = \begin{bmatrix} 0.6 \\ -1.0 \end{bmatrix},$$

$$u_{1} = \begin{bmatrix} 1.0 \\ -0.9 \end{bmatrix}, \quad T_{1} = \begin{bmatrix} -1.0 \\ -1.0 \end{bmatrix},$$

The number of response evaluations required in order to obtain these approximations is 45. This is the same as the number of coefficients of the quadratic polynomial, see equation (20) of Part I, for this 8-dimensional problem.

The weight assigned for each orthocell is obtained by multiplying the corresponding weight resulting from the correlations between the transistor model parameters, given in Table III, by the weights for the remaining uniformly distributed independent parameters. For a uniformly distributed parameter we have

$$w_{i}(0) = w_{i}(2) = 0.0,$$

$w_{i}(1) = 1.0.$

The yield sensitivities required during optimization are evaluated using equation (69) of Part I.

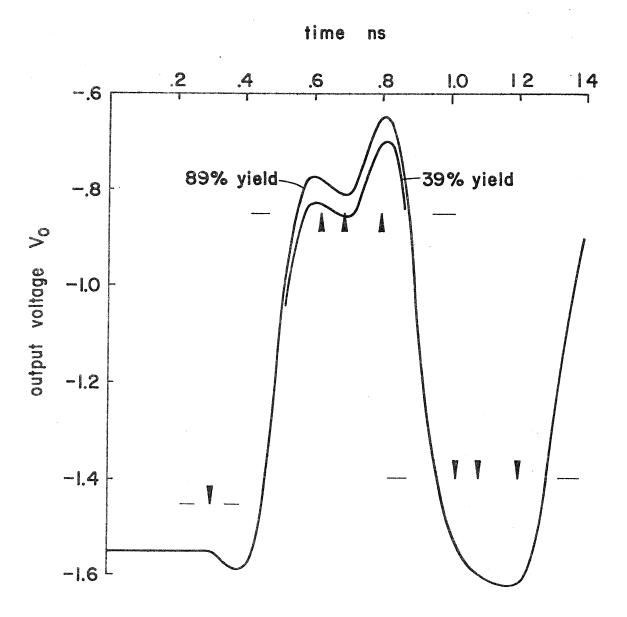

The results obtained for two different upper bounds on the characteristic impedance  $\mathbf{Z}_0$  are shown in Table V. These results may be compared with those obtained from 1000 Monte Carlo points, generated according to the assumed statistical distribution in conjunction with the quadratic approximations. The resulting yields are also tabulated in Table V and the nominal responses at the starting point and at the optimal solution are shown in Fig. 7.

In order to further demonstrate the benefits of having an approximation, different specifications were assumed and the corresponding yield optimiztions were carried out. The specified switching levels were varied as tabulated in Table VI and hence the corresponding constraints are simply generated by changing the constant term in the quadratic approximations. The resulting optimum yields and corresponding nominal values for the circuit parameters are given in Table VI.

The design constraints at t=1.02 ns and at t=1.09 ns were found to be overlapping. This is simply discovered by checking the reference vertices and the corresponding distances from them to the points of intersection of the linear cuts with the orthotope edges which are given by equations (43) and (45) of Part I, respectively. The constraint at t=1.02 ns was removed from the optimization process since it has the same reference vertex as the constraint at t=1.09 and its contribution to the weighted nonfeasible hypervolume is negligible.

#### V. CONCLUSIONS

Yield optimization of the CSEF circuit has been successfully performed. It has been demonstrated how small a number of simulations

is required: 75 integrations for the whole investigation. A summary of the effort is shown in Table VII. This number of simulations is much smaller than the number of Monte Carlo analyses, used in such a case, to provide even a single yield estimate let alone a complete optimization. Less than one second was required to carry out a complete yield and yield sensitivity evaluation, while more than 1.5 seconds are generally required for only one numerical integration using Gear's method.

Having approximations to the design constraints allowed us to consider different design specifications without any additional circuit simulations as seen from Table VII. Furthermore, different statistical distributions can be investigated. Similar transistors manufactured under different physical conditions, for example, can be readily investigated for optimum yield without additional integrations.

Finally, the reader may be interested in a recent review [23] of the authors' approach involving linear cuts based on quadratic approximations with the simplicial approximation approach originally devised by Director and Hachtel [24,25].

#### APPENDIX

# TOPOLOGICAL FORMULATION OF THE STATE EQUATIONS FOR THE CSEF CIRCUIT

The basic steps required in the formulation of the state equations for nonlinear networks are sketched out. For further details see Chua and Lin [26].

Step 1 Formation and characterization of network branches

This step involves the characterization of linear and nonlinear elements, controlled and independent sources and tree and cotree (link) branches. The choice of the tree branches is based upon

- (i) all independent and controlled voltage sources,

- (ii) as many capacitors as possible,

- (iii) as many resistors as possible,

- (iv) as few inductors as possible,

- (v) no independent current sources.

#### Step 2 Solving the resistive nonlinear subnetwork

We solve for the voltages across the nonlinear resistors in the tree as well as the currents in the nonlinear resistors in the cotree.

Step 3 Solving the loops which include capacitors only and the cutsets which include inductors only

In this step we express the currents in the cotree capacitors and the voltages across the tree inductors in terms of the derivatives (w.r.t. time) of the tree capacitor voltages and the cotree inductor currents. Also, they may well be functions of the derivatives of voltages of the tree independent voltage sources and derivatives of currents of cotree independent current sources (if these derivatives exist).

Step 4 Collecting relationships derived so far to formulate the state equations.

Regarding the CSEF circuit shown in Fig. 2, the input and output circuits can be treated independently.

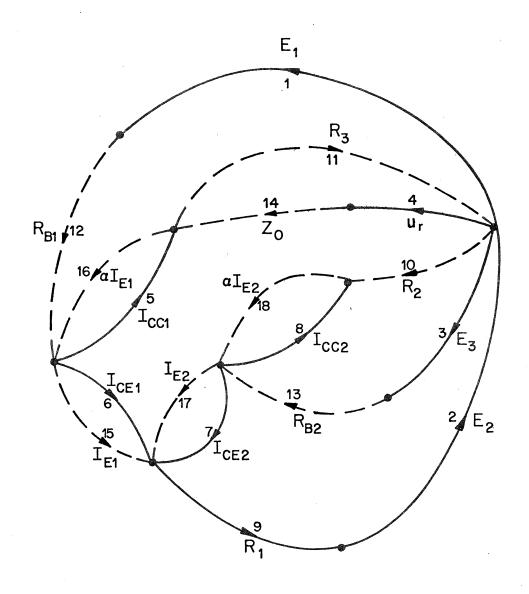

## A.1 Formulation of the State Equations for the Input Circuit

The tree chosen according to the priorities mentioned before is shown in Fig. A.1. According to this tree, the set of independent KCL equations is

$$\dot{\mathbf{I}} = \begin{bmatrix} \mathbf{I}_{\sim} \mathbf{ET} \\ \mathbf{I}_{\sim} \mathbf{CT} \\ \mathbf{I}_{\sim} \mathbf{RT} \\ \mathbf{I}_{\sim} \mathbf{RL} \\ \mathbf{I}_{\sim} \mathbf{JL} \end{bmatrix}, \tag{A.2}$$

$$I_{\text{ET}} \stackrel{\Delta}{=} \text{Tree voltage source currents} = \begin{bmatrix} I_1 \\ I_2 \\ I_3 \\ I_4 \end{bmatrix}$$

, (A.3)

$$I_{\text{CT}} \stackrel{\triangle}{=} \text{Tree capacitor currents} = \begin{bmatrix} I_5 \\ I_6 \\ I_7 \\ I_8 \end{bmatrix}, \qquad (A.4)$$

$$I_{RT} \stackrel{\triangle}{=} Tree resistor currents = [I_9] ,$$

(A.5)

$$I_{RL} \stackrel{\Delta}{=} Link resistor currents = \begin{bmatrix} I_{10} \\ I_{11} \\ I_{12} \\ I_{13} \\ I_{14} \end{bmatrix}, \qquad (A.6)$$

$$I_{JL} \stackrel{\Delta}{=} Link current sources = \begin{bmatrix} I_{15} \\ I_{16} \\ I_{17} \\ I_{18} \end{bmatrix}$$

(A.7)

and where

Hence, we can write (A.1) as

$$\mathbb{D}_{11} = \begin{bmatrix}

-1 & -1 & -1 \\

-1 & 1 & -1 & -1 \\

& -1 & -1

\end{bmatrix},

\tag{A.10}$$

$$D_{12} = 0$$

, (A.11)

$$D_{21} = \begin{bmatrix} -1 & 1 \\ 1 & -1 & -1 \\ -1 & -1 \end{bmatrix}, \qquad (A.12)$$

$$D_{22} = \begin{bmatrix} -1 \\ 1 \\ 1 \\ -1 \end{bmatrix}, \qquad (A.13)$$

$$_{-31}^{D} = [-1 \quad 1 \quad -1 \quad -1], \qquad (A.14)$$

$$^{D}_{32} = 0$$

(A.15)

and  $1_{9}$  is the identity matrix of order 9.

The KVL equations can be written as

$$\begin{bmatrix} D_{11}^{T} & D_{21}^{T} & D_{31}^{T} \\ D_{12}^{T} & D_{22}^{T} & D_{32}^{T} \end{bmatrix} - \mathbb{1}_{9} \end{bmatrix} \begin{bmatrix} \mathbf{v}_{ET} \\ \mathbf{v}_{CT} \\ \mathbf{v}_{RT} \\ \mathbf{v}_{RL} \\ \mathbf{v}_{JL} \end{bmatrix} = 0, \quad (A.16)$$

where superscript T denotes transposition.

It is required to represent the link currents  $\underline{I}_{RL}$  in terms of  $\underline{V}_{ET}$  and  $\underline{V}_{CT}.$  We have

$$\tilde{V}_{RL} = \tilde{R}_{L} \tilde{I}_{RL}$$

$$= D_{11}^{T} v_{ET} + D_{21}^{T} v_{CT} + D_{31}^{T} v_{RT}, \qquad (A.17)$$

where

$${}_{L}^{R} = \begin{bmatrix} {}^{R}_{2} & & & & & & & \\ & {}^{R}_{3} & & & & & \\ & & {}^{R}_{B1} & & & & \\ & & & {}^{R}_{B2} & {}^{Z}_{0} \end{bmatrix}.$$

(A.18)

Using (A.9) and (A.15) we can write

$$I_{RT} = -D_{31} I_{RL} - D_{32} I_{JL}$$

$$= -D_{31} I_{RL} . \qquad (A.19)$$

Thus,

$$V_{RT} = R_T I_{RT} = -R_T D_{31} I_{RL}$$

, (A.20)

where

$$R_{T} = [R_1] . \tag{A.21}$$

Substituting for  $V_{\mbox{\scriptsize RT}}$  in (A.17) and with some manipulations, we obtain

$$I_{RL} = R^{-1} \left[ D_{11}^{T} V_{ET} + D_{21}^{T} V_{CT} \right],$$

(A.22)

where

$$R = R_{L} + D_{31}^{T} R_{T} D_{31}.$$

(A.23)

From (A.5), we have

$$I_{\text{CT}} = -D_{21} I_{\text{RL}} - D_{22} I_{\text{JL}}$$

(A.24)

Substituting for  $I_{\rm RL}$  from (A.22), the state equations are

$$I_{CT} = -D_{21} R^{-1} [D_{11}^{T} V_{ET} + D_{21}^{T} V_{CT}] - D_{22} I_{JL}$$

(A.25)

More explicitly, they can be written as

$$\begin{bmatrix} C_{C1} & dV_{C1}/dt \\ C_{E1} & dV_{BE1}/dt \\ C_{E2} & dV_{BE2}/dt \\ C_{C2} & dV_{C2}/dt \end{bmatrix} = -D_{21} R^{-1} \begin{bmatrix} D_{11}^{T} & E_{1} \\ D_{11}^{T} & E_{2} \\ E_{3} \\ u_{r} \end{bmatrix} + D_{21}^{T} \begin{bmatrix} V_{C1} \\ V_{BE1} \\ V_{BE2} \\ V_{C2} \end{bmatrix} + \begin{bmatrix} I_{16} \\ -I_{15} \\ -I_{17} \\ I_{18} \end{bmatrix}, \quad (A.26)$$

where

$$C_{E1} = C_{JE} + TT \theta I_S \exp(\theta V_{BE1})$$

, (A.27)

$$C_{E2} = C_{JE} + TT \theta I_S \exp(\theta V_{BE2})$$

, (A.28)

$$I_{15} = I_{S}(\exp(\theta \ V_{BE1})-1)$$

, (A.29)

$$I_{16} = \alpha I_{15}$$

, (A.30)

$$I_{17} = I_{S}(\exp(\theta \ V_{BE2})-1)$$

, (A.31)

$$I_{18} = \alpha I_{17}$$

(A.32)

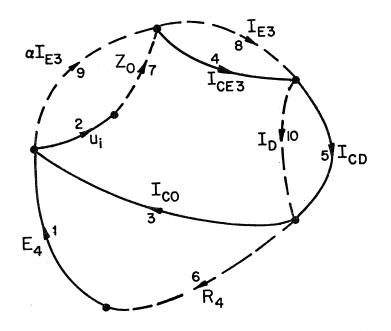

### A.2 Formulation of the State Equations for the Output Circuit

Figure A.2 shows the chosen tree and branch numbering. The set of independent KCL equations is

$$D_{\tilde{a}} = 0$$

, (A.33)

$$\dot{\mathbf{i}} = \begin{bmatrix} \mathbf{I}_{ET} \\ \mathbf{I}_{CT} \\ \mathbf{I}_{RL} \\ \mathbf{I}_{JL} \end{bmatrix}, \qquad (A.35)$$

$$I_{\text{ET}} \stackrel{\triangle}{=} \text{Tree voltage source currents} = \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

, (A.36)

$$I_{\text{CT}} \stackrel{\triangle}{=} \text{Tree capacitor currents} = \begin{bmatrix} I_3 \\ I_4 \\ I_5 \end{bmatrix}, \qquad (A.37)$$

$$I_{RL} \stackrel{\triangle}{=} Link resistor currents = \begin{bmatrix} I_6 \\ I_7 \end{bmatrix}, \qquad (A.38)$$

$$I_{JL} \stackrel{\Delta}{=} Link current sources = \begin{bmatrix} I_8 \\ I_9 \\ I_{10} \end{bmatrix}. \tag{A.39}$$

The KVL equations are

Hence,

$$V_{RL} = R_{L} I_{RL}$$

$$= D_{11}^{T} V_{ET} + D_{21}^{T} V_{CT}, \qquad (A.41)$$

$${\stackrel{R}{\sim}} L = \begin{bmatrix} {\stackrel{R}{\downarrow}} & & \\ & Z_0 \end{bmatrix}, \qquad (A.42)$$

$$D_{11} = \begin{bmatrix} -1 \\ -1 \end{bmatrix}, \qquad (A.43)$$

$$D_{21} = \begin{bmatrix} 1 & -1 \\ -1 \\ -1 \end{bmatrix}. \tag{A.44}$$

Thus,

$$I_{RL} = R_L^{-1} [D_{11}^T V_{ET} + D_{21}^T V_{CT}].$$

(A.45)

From (A.33), we have

$$I_{\text{ET}} = -D_{11} I_{\text{RL}}$$

(A.46)

and

$$I_{CT} = -D_{21} I_{RL} - D_{22} I_{JL}$$

(A.47)

Substituting for  $I_{RL}$  from (A.45) into (A.47), the state equations are

$$I_{\text{CT}} = -D_{21} R_{\text{L}}^{-1} \left[ D_{11}^{\text{T}} V_{\text{ET}} + D_{21}^{\text{T}} V_{\text{CT}} \right] - D_{22} I_{\text{JL}}.$$

(A.48)

Or, more explicitly, the state equations are

$$\begin{bmatrix} c_{0} & dv_{0}/dt \\ c_{E3} & dv_{BE3}/dt \\ c_{D} & dv_{D}/dt \end{bmatrix} = -D_{21} \begin{bmatrix} 1/R_{4} \\ 1/Z_{0} \end{bmatrix} \begin{bmatrix} D_{11}^{T} & D_{21}^{T} \\ V_{0} \\ V_{BE3} \\ V_{D} \end{bmatrix} + \begin{bmatrix} I_{9} \\ I_{9}-I_{8} \\ I_{9}-I_{10} \end{bmatrix}, (A.49)$$

$$C_{E3} = C_{JE} + TT \theta I_S \exp(\theta V_{BE3})$$

, (A.50)

$$C_D = C_{JD} + TT_D \theta I_{SD} \exp(\theta V_D)$$

, (A.51)

$$I_8 = I_S (\exp(\theta \ V_{BE3})-1)$$

, (A.52)

$$I_9 = \alpha I_8 , \qquad (A.53)$$

$$I_{10} = I_{SD} (\exp(\theta \ V_D) - 1)$$

(A.54)

If the diode is similar to the transistor base emitter junction, then

$$V_{D} = V_{BE3} \tag{A.55}$$

and

$$I_{10} = I_8$$

(A.56)

Hence, the three state equations (A.49) can be reduced to the following two equations

$$\begin{bmatrix} c_0 & dV_0/dt \\ c_{E3} & dV_{BE3}/dt \end{bmatrix} = \begin{bmatrix} -1 & 1 \\ & 1 \end{bmatrix} \begin{bmatrix} 1/R_{4} \\ & & \\ & 1/Z_0 \end{bmatrix} + \begin{bmatrix} -1 & 1 & 1 \\ & & \\ & & -1 & -1 & -2 \end{bmatrix} \begin{bmatrix} u_1 \\ v_0 \\ v_{BE3} \end{bmatrix} + \begin{bmatrix} I_9 \\ I_9 - I_8 \end{bmatrix} . \quad (A.57)$$

#### ACKNOWLEDGEMENTS

The authors wish to thank Dr. C.W. Ho, IBM Research Labs, Yorktown Heights, N.Y., who made available some unpublished information on the CSEF circuit. The authors also wish to thank M.R.M. Rizk for verifying the simulation of the CSEF circuit by an independent analysis.

#### REFERENCES

- [1] H.L. Abdel-Malek and J.W. Bandler, "Yield optimization for arbitrary statistical distributions, Part I: Theory", published in conjunction with the present paper.

- [2] B.J. Karafin, "The optimum assignment of component tolerances for electrical networks", <u>BSTJ</u>, vol. 50, 1971, pp. 1225-1242.

- [3] E.M. Butler, "Realistic design using large-change sensitivities and performance contours", <u>IEEE Trans. Circuit Theory</u>, vol. CT-18, Jan. 1971, pp. 58-66.

- [4] J.W. Bandler and P.C. Liu, "Automated network design with optimal tolerances", <u>IEEE Trans. Circuits and Systems</u>, vol. CAS-21, March 1974, pp. 922-931.

- [5] H.L. Abdel-Malek and J.W. Bandler, "Yield estimation for efficient design centering assuming arbitrary statistical distributions", <u>Int. J. Circuit Theory and Applications</u>, vol. 6, 1978, pp. 289-303.

- [6] J.W. Bandler, P.C. Liu and J.H.K. Chen, "Worst case network tolerance optimization", <u>IEEE Trans. Microwave Theory Tech.</u>, vol. MTT-23, Aug. 1975, pp. 630-641.

- [7] J.W. Bandler, P.C. Liu and H. Tromp, "A nonlinear programming approach to optimal design centering, tolerancing and tuning", <u>IEEE Trans. Circuits and Systems</u>, vol. CT-23, March 1976, pp. 155-165.

- [8] J.W. Bandler and H.L. Abdel-Malek, "Optimal centering, tolerancing and yield determination via updated approximations and cuts", <u>IEEE Trans. Circuits and Systems</u>, vol. CAS-25, Oct. 1978, pp. 853-871.

- [9] N.J. Elias, "New statistical methods for assigning device tolerances", <u>Proc. 1975 IEEE Symp. on Circuits and Systems</u> (Newton, MA, April 1975), pp. 329-332.

- [10] P.W. Becker and F. Jensen, <u>Design of Systems and Circuits for Maximum Reliability or Maximum Production Yield</u>. Lyngby: Polyteknisk Forlag, 1974.

- [11] R.K. Brayton, G.D. Hachtel and S.W. Director, "Arbitrary norms for statistical design via linear programming", <u>Proc. 1978 IEEE Int. Symp. on Circuits and Systems</u> (New York, NY, May 1978), pp. 161-164.

- [12] C.W. Ho, "Time-domain sensitivity computation for networks containing transmission lines", <u>IEEE Trans. Circuit Theory</u>, vol. CT-18, Jan. 1971, pp. 114-122.

- [13] P. Balaban and J.J. Golembeski, "Statistical analysis for

- practical circuit design", <u>IEEE Trans. Circuits and Systems</u>, vol. CAS-22. Feb. 1975, pp. 100-108.

- [14] D.A. Calahan, <u>Computer-aided Network Design</u> (Revised Edition).

New York: McGraw-Hill, 1972.

- [15] H.L. Abdel-Malek and J.W. Bandler, "State equation analysis and computer program for a current switch emitter follower", Faculty of Engineering, McMaster University, Hamilton, Canada, Report SOC-192, 1978.

- [16] Subroutine DVOGER, International Mathematical and Statistical Libraries, IMSL Library 3, Edition 5, (FORTRAN) CDC 6000/7000, 1975.

- [17] C.W. Gear, "The automatic integration of differential equations", Comm. ACM., vol. 14, March 1971, pp. 176-179.

- [18] M.R.M. Rizk, "Analysis of a current switch emitter follower using the companion network approach", Faculty of Engineering, McMaster University, Hamilton, Canada, Report SOC-193, 1978.

- [19] H.L. Abdel-Malek and J.W. Bandler, "Subroutines for implementing quadratic models of surfaces in optimal design", Faculty of Engineering, McMaster University, Hamilton, Canada, Report SOC-191, 1978.

- [20] J.W. Bandler and C. Charalambous, "Nonlinear programming using minimax techniques", <u>J. Optimization Theory and Applications</u>, vol. 13, June 1974, pp. 607-619.

- [21] J.W. Bandler and D. Sinha, "FLOPT4 a program for least pth optimization with extrapolation to minimax solutions", Faculty of Engineering, McMaster University, Hamilton, Canada, Report SOC-151, 1977.

- [22] E.M. Butler, "Techniques for statistical DC modeling of bipolar transistors", <u>Proc. 1974 IEEE Symp. on Circuits and Systems</u> (San Francisco, CA, April 1974), pp. 725-729.

- [23] J.W. Bandler and H.L. Abdel-Malek, "Algorithms for design centering involving yield and its sensitivities", <u>Proc. 21st Midwest Symp. on Circuits and Systems</u> (Ames, IA, Aug. 1978), pp. 242-248.

- [24] S.W. Director and G.D. Hachtel, "The simplicial approximation approach to design centering", <u>IEEE Trans. Circuits and Systems</u>, vol. CAS-24, July 1977, pp. 363-372.

- [25] S.W. Director, G.D. Hachtel and L.M. Vidigal, "Computationally efficient yield estimation procedures based on simplicial approximation", <u>IEEE Trans. Circuits and Systems</u>, vol. CAS-25, 1978, pp. 121-130.

[26] L.O. Chua and P.M. Lin, <u>Computer-aided Analysis of Electronic Circuits</u>. Englewood Cliffs, NJ: Prentice-Hall, 1975.

TABLE I(a)

CIRCUIT PARAMETER VALUES

| R <sub>1</sub> | 281.33 Ω |

|----------------|----------|

| R <sub>2</sub> | 75.00 Ω  |

| <sup>R</sup> 3 | 78.24 Ω  |

| R <sub>4</sub> | 50.00 Ω  |

| E <sub>2</sub> | 4.03 V   |

| E <sub>3</sub> | 1.13 V   |

| E4             | 1.70 V   |

| co             | 1.50 pF  |

TABLE I(b)

DIODE MODEL PARAMETERS

| I <sub>SD</sub>                 | diode saturation current              | $0.6 \times 10^{-9} A$  |

|---------------------------------|---------------------------------------|-------------------------|

| $c^{DD}$                        | depletion layer capacitance           | 0.12 pF                 |

| $\mathtt{TT}_{\mathtt{D}}$      | transit time                          | 0.01 ns                 |

| θ .                             | inverse of thermal potential          | $38.668 \text{ v}^{-1}$ |

|                                 |                                       |                         |

| $I_D = I_S$                     | $_{\rm SD}(\exp(\theta V_{\rm D})-1)$ |                         |

| C <sub>D</sub> = C <sub>J</sub> | $_{D} + TT_{D} \frac{dI_{D}}{dV_{D}}$ |                         |

TABLE I(c)

TRANSISTOR MODEL PARAMETERS

| Is                                           | saturation current                           | $0.6 \times 10^{-9} A$ |  |  |  |  |

|----------------------------------------------|----------------------------------------------|------------------------|--|--|--|--|

| α                                            | common base current gain                     | 0.99                   |  |  |  |  |

| $R_{\mathbf{B}}$                             | base resistance                              | 50.0 Ω                 |  |  |  |  |

| СС                                           | collector junction capacitance               | 0.5 pF                 |  |  |  |  |

| C <sub>JE</sub>                              | emitter junction depletion layer capacitance | 0.12 pF                |  |  |  |  |

| TT                                           | base transit time                            | 0.01 ns                |  |  |  |  |

| θ                                            | inverse of thermal potential                 | 38.668 V <sup>-1</sup> |  |  |  |  |

| I <sub>E</sub> = I                           | S (exp(θV <sub>BE</sub> )-1)                 |                        |  |  |  |  |

| $I_C = \alpha$                               | IE                                           |                        |  |  |  |  |

| $C_{E} = C_{JE} + TT \frac{dI_{E}}{dV_{BE}}$ |                                              |                        |  |  |  |  |

| $R_{\mathrm{B}}$ and                         | C <sub>C</sub> are assumed zero for transis  | tor T <sub>3</sub>     |  |  |  |  |

TABLE I(d)

TRANSMISSION LINE PARAMETERS

| z <sub>o</sub> | characteristic impedance | 50 Ω    |

|----------------|--------------------------|---------|

| τ              | delay time               | 0.25 ns |

TABLE II

WORST-CASE DESIGN FOR THE CSEF CIRCUIT

| E <sub>4</sub> (V) | z <sub>0</sub><br>(Ω) | R <sub>4</sub> <sup>0</sup> (Ω) | C <sub>0</sub><br>(pF) |      | ε <sub>2</sub> /Z <sub>0</sub><br>(%) | ε <sub>3</sub> /R <sub>4</sub><br>(%) | ε <sub>4</sub> /C <sub>0</sub> (%) |

|--------------------|-----------------------|---------------------------------|------------------------|------|---------------------------------------|---------------------------------------|------------------------------------|

| 1.655              | 92.004                | 45.533                          | 1.248                  | 4.46 | 8.29                                  | 13.77                                 | 14.00                              |

Objective cost function  $\sum_{i=1}^{4} \phi_{i}^{0}/\epsilon_{i}$

Number of complete response evaluations = 30

CDC modeling time = 48 s

CDC time (approximation and optimization) = 103 s

TABLE III  $\mbox{RESULTING WEIGHTS DUE TO CORRELATION BETWEEN B, I_S \mbox{ AND } C_{\mbox{\bf JE}}$

|                                 | β      | α                             | $c_{JE}^{**}$ $c_{I_S}^{**}$ , $i = 0.221 \times 10^{-9} A$ $c_{JE}^{**}$ , $i = 0.60$ |                |        |                | $I_{S}$ ** $I_{S}$ , i = 0.221x10 <sup>-9</sup> A $\epsilon_{C_{J}}$ |                  |        | :18 pF |

|---------------------------------|--------|-------------------------------|----------------------------------------------------------------------------------------|----------------|--------|----------------|----------------------------------------------------------------------|------------------|--------|--------|

| ε <sub>β</sub> , i <sub>β</sub> | W      | <sup>ε</sup> α,i <sub>α</sub> | W                                                                                      | w <sub>1</sub> | ₩2     | w <sub>3</sub> | w <sub>1</sub>                                                       | , w <sub>2</sub> | ₩3     |        |

| 20.0                            | 0.3333 | 0.0080                        | 0.3333                                                                                 | 0.8320         | 0.1680 | 0.0000         | 0.2345                                                               | 0.4084           | 0.3571 |        |

| 20.0                            | 0.5000 | 0.0041                        | 0.5000                                                                                 | 0.3599         | 0.6113 | 0.0288         | 0.3174                                                               | 0.4258           | 0.2568 |        |

| 20.0                            | 0.1667 | 0.0024                        | 0.1667                                                                                 | 0.0744         | 0.5731 | 0.3525         | 0.4059                                                               | 0.4472           | 0.1469 |        |

<sup>\*</sup>  $\alpha = \beta/(\beta+1)$

<sup>\*\*</sup> Equal intervals for  $I_S$  and  $C_{JE}$  are considered Lower extremes of the parameters are  $\beta$  = 40.0,  $\alpha$  = 0.9756,  $I_S$  = 0.1582×10<sup>-9</sup> A and  $C_{JE}$  = 0.0958 pF

TABLE IV

INTERPOLATION REGION SIZE AND CENTER

FOR THE CSEF EXAMPLE

|        | Е <sub>4</sub><br>(V) | Z <sub>0</sub> (Ω) | R <sub>4</sub> | C <sub>0</sub> | <sup>α</sup> 3 | <sup>I</sup> S3<br>(10 <sup>-9</sup> A) | C <sub>JE3</sub> | TT <sub>3</sub> |

|--------|-----------------------|--------------------|----------------|----------------|----------------|-----------------------------------------|------------------|-----------------|

| ₹      | 1.632                 | 95.0               | 44.0           | 1.35           | 0.98285        | 0.49135                                 | 0.1285           | 0.0100          |

| δ<br>~ | 0.170                 | 15.0               | 10.0           | 0.45           | 0.00786        | 0.34400                                 | 0.0380           | 0.0025          |

TABLE  $\mathbf{V}$  RESULTS FOR THE MAXIMIZATION OF YIELD FOR THE CSEF CIRCUIT

|                                   | E <sub>4</sub> | z <sub>o</sub> | R <sub>Ц</sub> | c <sub>0</sub> | Optimization | Yield (%)     |      |

|-----------------------------------|----------------|----------------|----------------|----------------|--------------|---------------|------|

| Description                       | (V)            | (Ω)            | (Ω)            | (pF)           | time<br>(s)  | Linear<br>Cut | M.C. |

| Starting values                   | 1.632          | 95.00          | 44.00          | 1.35           | -            | 25.7          | 39.4 |

| Optimum for $Z_{Ou} = 100 \Omega$ | 1.595          | 100.00         | 51.15          | 1.27           | 67.8         | 58.6          | 68.9 |

| Optimum for $Z_{Ou} = 105 \Omega$ | 1.638          | 105.00         | 53.07          | 1.27           | 40.6         | 85.6          | 89.1 |

CDC modeling time = 74 s

CDC time required for M.C. employing approximation  $\simeq$  5 s

TABLE VI

YIELD OPTIMIZATION FOR DIFFERENT SPECIFICATIONS

| Specifications |        | E 4   | z <sub>0</sub> | R <sub>4</sub> 0 | c <sub>0</sub> | Yield (%)  |

|----------------|--------|-------|----------------|------------------|----------------|------------|

| , а            | Ъ      | (V)   | (Ω)            | (Ω)              | (pF)           | Linear Cut |

| -1.450         | -0.900 | 1.657 | 90.00          | 51.84            | 1.27           | 65.1       |

| -1.425         | -0.925 | 1.652 | 90.00          | 48.95            | 1.27           | 91.4       |

| -1.400         | -0.950 | 1.637 | 90.00          | 44.91            | 1.27           | 99.7       |

$V_0(t) \le a V$ , t = 0.3, 1.02, 1.09, 1.2 ns

$Z_{Ou} = 90 \Omega$

$V_0(t) \ge b V$ , t = 0.62, 0.69, 0.8 ns

TABLE VII

SUMMARY OF EFFORT FOR THE CSEF

| Optimization                             |             | Number of yield | CDC time |              |  |

|------------------------------------------|-------------|-----------------|----------|--------------|--|

| problem                                  | simulations | evaluations     | modeling | optimization |  |

| worst-case                               | 30          | 0               | 48 s     | 55 s         |  |

| yield                                    | 75          | 49              | 122 s    | 96 s         |  |

| perturbed constraints and specifications | 0           | ~ 50            | 0        | ~ 45 s       |  |

#### FIGURE CAPTIONS

- Fig. 1 The CSEF circuit [12].

- Fig. 2 The CSEF equivalent circuit used, indicating transmission line, transistor and diode models.

- Fig. 3 Original, nominal and worst-case responses of the CSEF.

- Fig. 4 Assumed distribution for the transistor current gain β.

- Fig. 5 Illustration of the assumed discretized joint distribution of the transistor common base current gain  $\alpha$  and the saturation current  $I_{\tilde{S}}$ . Appropriate weights of Table III divided by the corresponding cell area give the values of the PDF.

- Fig. 6 Illustration of the assumed discretized joint distribution of the transistor common base current gain  $\alpha$  and the emitter junction depletion layer capacitance  $C_{JE}$ . Appropriate weights of Table III divided by the corresponding cell area give the values of the PDF.

- Fig. 7 Nominal responses of the CSEF corresponding to the 39% yield and 89% yield entries of Table V.

- Fig. A.1 Directed graph of the input circuit and branch numbering.

\_\_\_\_ Tree chosen

---- Corresponding link

- Fig. A.2 Directed graph of the output circuit and branch numbering.

\_\_\_\_ Tree chosen

--- Corresponding link

Fig. 1

- 36 -

Fig. 3

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig. A.1

Fig. A.2

|  |  |  | ٧ |

|--|--|--|---|

|  |  |  | £ |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  | • |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  | b |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

|  |  |  |   |

SOC-185

YIELD OPTIMIZATION FOR ARBITRARY STATISTICAL DISTRIBUTIONS PART II: IMPLEMENTATION

H.L. Abdel-Malek and J.W. Bandler

November 1977, No. of Pages: 43

Revised: June 1978, March 1979

Key Words: Yield analysis, design centering, tolerance assignment,

numerical integration, nonlinear network design

Abstract: A suggested test problem for proposed algorithms in yield optimization is described in detail. The problem is a current switch emitter follower (CSEF) circuit originally described by Ho, which includes a transmission line. The ideas presented in Part I of this paper are applied to this circuit in order to obtain an optimal statistical design. Production yield is maximized taking into consideration statistical distributions of circuit parameters and realistic correlations between transistor model parameters. Nonlinear programming employing the analytical formulas for yield and its sensitivities is used to provide optimal nominal values for the circuit parameters. Different design specifications are assumed and corresponding optimal designs are obtained.

Description: Presented at the IEEE International Symposium on

Circuits and Systems (New York, May 1978). See the

symposium proceedings, pp. 670-674.

Related Work: SOC-182, SOC-184, SOC-191, SOC-192, SOC-193, SOC-194.

Price: \$ 6.00.