# SIMULATION OPTIMIZATION SYSTEMS Research Laboratory

### COST-DRIVEN PHYSICS-BASED LARGE-SIGNAL SIMULTANEOUS DEVICE AND CIRCUIT DESIGN

J.W. Bandler, R.M. Biernacki, Q. Cai and S.H. Chen

SOS-94-9-V

May 1995

### COST-DRIVEN PHYSICS-BASED LARGE-SIGNAL SIMULTANEOUS DEVICE AND CIRCUIT DESIGN

J.W. Bandler, R.M. Biernacki, Q. Cai and S.H. Chen

SOS-94-9-V

May 1995

© J.W. Bandler, R.M. Biernacki, Q. Cai and S.H. Chen 1995

No part of this document may be copied, translated, transcribed or entered in any form into any machine without written permission. Address enquiries in this regard to Dr. J.W. Bandler. Excerpts may be quoted for scholarly purposes with full acknowledgement of source. This document may not be lent or circulated without this title page and its original cover.

|  |  | 4 |

|--|--|---|

|  |  | 8 |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | 4 |

|  |  | 6 |

|  |  | ₩ |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | æ |

|  |  | 9 |

|  |  |   |

|  |  |   |

|  |  |   |

### COST-DRIVEN PHYSICS-BASED LARGE-SIGNAL SIMULTANEOUS DEVICE AND CIRCUIT DESIGN

J.W. Bandler, R.M. Biernacki, Q. Cai and S.H. Chen

Simulation Optimization Systems Research Laboratory and Department of Electrical and Computer Engineering McMaster University, Hamilton, Canada L8S 4L7

|  |  | ¢  |

|--|--|----|

|  |  | P  |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  | 8  |

|  |  | •  |

|  |  | ·  |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  |    |

|  |  | 4  |

|  |  | \$ |

|  |  |    |

|  |  |    |

|  |  |    |

We present a cost-driven approach to the emerging demand for simultaneous device and circuit design. Here, an analytic physics-based Raytheon model facilitates fast large-signal simulation and optimization. A novel one-sided Huber approach is applied to design centering. The problem of cost-driven design is formulated as the minimization of the cost function while maintaining the required yield. Devices and matching circuits are optimized simultaneously, the advantages of which are demonstrated by a single-stage power amplifier design.

#### Introduction

random variations in the manufacturing process may lead to some circuits violating design specifications

manufacturing cost and production yield depend on circuit parameters such as nominal values, tolerances and uncertainties

cost-effective yield-driven design is a challenge in microwave CAD, particularly, in MMIC design

CAD systems must link geometry, layout, physical and process parameters with performance, yield and system specifications to address this challenge

utilization of physical models and physics-based models is the key to meet the requirement of predictability and economization

first-pass success in a fabricated circuit meeting its design specifications can be a realistic goal

#### **Yield Optimization and Cost-Driven Design**

takes into account the manufacturing tolerances, model uncertainties, variations in the process parameters, environmental uncertainties, etc.

yield optimization maximizes yield by adjusting the nominal values of the design variables while keeping their tolerances constant

reducing tolerances increases yield but increases cost also: there is a trade-off between yield and cost

cost-driven design minimizes cost while maintaining the required yield

#### Physics-Based and Physical Device Models

physics-based models (PBMs)

relate the circuit elements to the device physics based on a simplified analytical solution of device equations

explicit analytical model equations (e.g., Pucel et. al, 1975, Chen and Shur, 1985, D'Agostino et. al, 1992)

solving for intermediate parameters may be required (e.g., Madjar and Rosenbaum, 1981, Khatibzadeh and Trew, 1988)

faster to compute but less accurate than physical models physical models (PMs)

based on the numerical solution of the fundamental device equations

typically employing finite-difference or finite-element techniques (e.g., Snowden et. al, 1983 and 1987)

the most accurate but computationally intensive

both PBMs and PMs are capable of performance prediction, permitting device optimization

#### Physics-Based Raytheon (PBR) Model

the model structure and the model equations follow the Raytheon model (Statz et. al, 1987)

the empirical parameters of the Raytheon model are calculated from the physical parameters using analytical formulas (D'Agostino et. al, 1992)

The PBR model is implemented in conjunction with the built-in Raytheon model (FETR) in OSA90/hope and HarPE

facilitates fast large-signal simulation and optimization, particularly useful for yield- and cost-driven design where a large number of outcomes need to be analyzed

# Design Centering Using the One-Sided Huber Function (Bandler, Chen, Biernacki and Madsen, 1994)

objective function for yield optimization using the one-sided Huber function

$$U(\phi^0) = \sum_{i=1}^N \rho_k^{\dagger} [\alpha_i \nu(\phi^i)]$$

where

$\phi^0$  vector of nominal circuit parameters  $\phi^i$  the *i*th statistical outcome  $(\phi^i = \phi^0 + \Delta \phi^i)$

$\alpha_i$  a positive multiplier associated with the *i*th outcome  $v(\phi^i)$  generalized  $\ell_p$  function

$\rho_k^{\dagger}$  the one-sided Huber function defined by

$$\rho_{k}^{+}(f) = \begin{cases} 0 & \text{if } f \leq 0 \\ f^{2}/2 & \text{if } 0 < f \leq k \\ kf - k^{2}/2 & \text{if } f > k \end{cases}$$

where

k a positive constant threshold value

f an error function which is  $\alpha_i v(\phi^i)$  in our case

#### Formulation of Cost-Driven Design

minimizes cost while maintaining the required yield

optimization problem for cost-driven design (Bandler and Abdel-Malek, 1978)

minimize

$$C(x)$$

subject to

$$Y \ge Y_S$$

where

x vector of parameter tolerances and/or standard deviations

Y design yield

$Y_S$  specified yield

C(x) cost function, e.g., (Karafin, 1971, Bandler, 1974)

$$C(x) = \sum_{i=1}^{m} \frac{c_i}{x_i}$$

maximize the parameter tolerances to minimize cost, since the larger the parameter tolerances the lower the cost

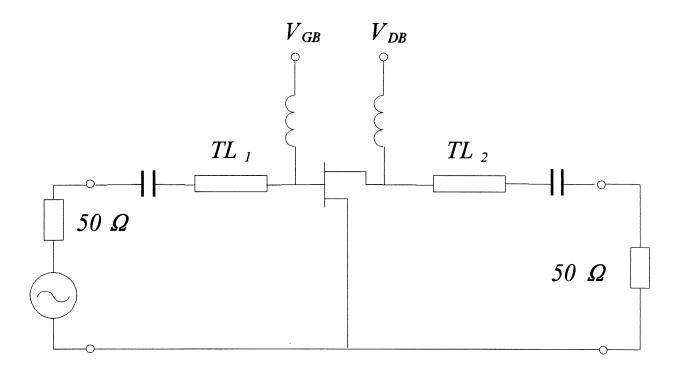

### A Single-Stage Power Amplifier Design

(OSA90/hope Applications Illustrated, 1994)

PBR is used to model the MESFET

nominal design, yield optimization and cost-driven design are performed using OSA90/hope

#### **Design Specification and Variables**

the design specifications

$$P_{out}[1] \ge 26 \text{ dBm}$$

$P_{out}[2] \le 4 \text{ dBm}$

$PAE \ge 30\%$

where

$P_{out}[1]$  the fundamental output power

$P_{out}[2]$  the second harmonic output power

*PAE* the power-added efficiency

#### design variables

#### **MESFET**

L gate length

Z gate width

a channel thickness

$N_d$  doping density

#### linear subcircuit

$TL_1$  length of the input line

$TL_2$  length of the output line

#### **Nominal Design**

minimax optimization

nominal design in two cases

#### Case I

the device (MESFET) is kept constant and the matching circuits ( $TL_1$  and  $TL_2$ ) are optimized

at the minimax solution only the specification for  $P_{out}[1]$  is satisfied; the specifications for  $P_{out}[2]$  and PAE are violated

#### Case II

both the device and the matching circuits are optimized starting at the solution of Case I

after optimization all the specifications are satisfied

the advantages of simultaneous device and circuit design over the conventional circuit design (only the matching circuits can be optimized) are clearly demonstrated

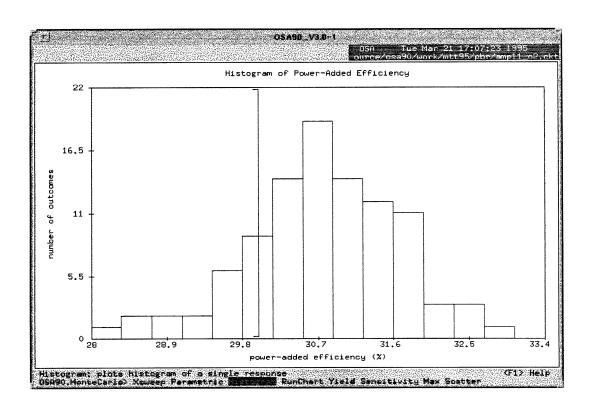

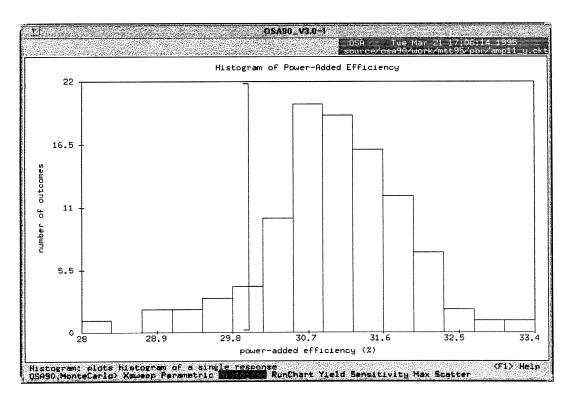

#### **Yield Optimization**

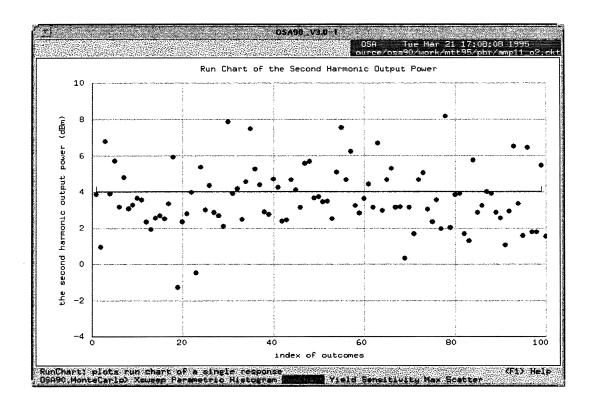

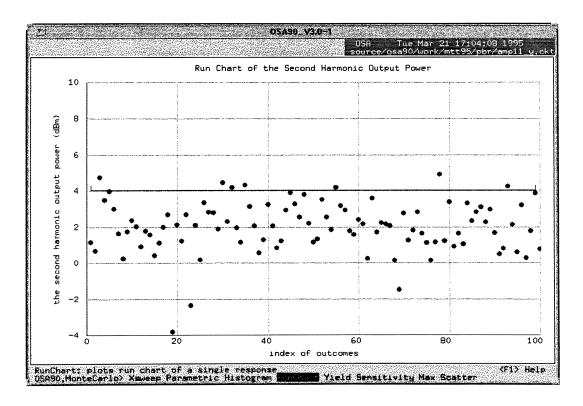

starting from the minimax solution of nominal design Case II using the one-sided Huber approach with 100 statistical outcomes

a normal distribution with 3% standard deviation is assigned to the physical parameters of the MESFET, the characteristic impedance and the lengths of the transmission lines

all statistical parameters are considered independent

yield is increased from 56% at the starting point to 83% after optimization

### Histograms of PAE Before and After Yield Optimization

# 0

### Run Chart of Pout[2] Before and After Yield Optimization

#### **Cost-Driven Design**

starting from the solution of design centering

#### design variables

$x_L$  standard deviation of FET gate length

$x_z$  standard deviation of FET gate width

$x_a$  standard deviation of FET channel thickness

$x_{Nd}$  standard deviation of FET doping density

$x_{TL}$  standard deviation of transmission lines  $TL_1$  and  $TL_2$

optimization is performed in five cases for specified yields of 80%, 75%, 70%, 65% and 60%

the weighting factors are selected as 3, 2, 5, 2 and 1 for  $x_L$ ,  $x_Z$ ,  $x_a$ ,  $x_{Nd}$  and  $x_{TL}$ , respectively

after optimization the standard deviations (in effect the manufacturing tolerances) are enlarged, consequently the costs are reduced

### Simulation Optimization Systems Research Laboratory McMaster University

#### STANDARD DEVIATIONS FOR COST-DRIVEN DESIGN

| Ctondord           | Defere                 | After Optimization |        |        |        |        |  |

|--------------------|------------------------|--------------------|--------|--------|--------|--------|--|

| Standard Deviation | Before<br>Optimization | Case 1             | Case 2 | Case 3 | Case 4 | Case 5 |  |

| x,(%)              | 3                      | 3.1152             | 3.2366 | 3.4590 | 3.7103 | 3.9781 |  |

| $X_{7}(\%)$        | 3                      | 3.0517             | 3.1075 | 3.2123 | 3.3351 | 3.4698 |  |

| $\chi_{a}(\%)$     | 3                      | 3.3098             | 3.6150 | 4.1467 | 4.7009 | 5.2722 |  |

| $\chi_{Nd}(\%)$    | 3                      | 3.0517             | 3.1075 | 3.2123 | 3.3351 | 3.4698 |  |

| $X_{\tau_l}(\%)$   | 3                      | 3.0130             | 3.0272 | 3.0545 | 3.0872 | 3.1241 |  |

Case 1: the specified yield is 80%.

Case 2: the specified yield is 75%.

Case 3: the specified yield is 70%.

Case 4: the specified yield is 65%.

Case 5: the specified yield is 60%.

#### **Conclusions**

physics-based large-signal simultaneous device and circuit design has advantages over conventional circuit design

robust physics-based one-sided Huber design centering can be used to optimize physical parameters to increase yield

cost-driven design by minimizing the cost function subject to a specified yield can be applied to find a compromise between yield and cost

physics-based models have certain limitations such as limited accuracy and the requirement of determining empirical fitting factors

physical models should be used for more accurate applications though they require significantly more computation time than the physics-based models

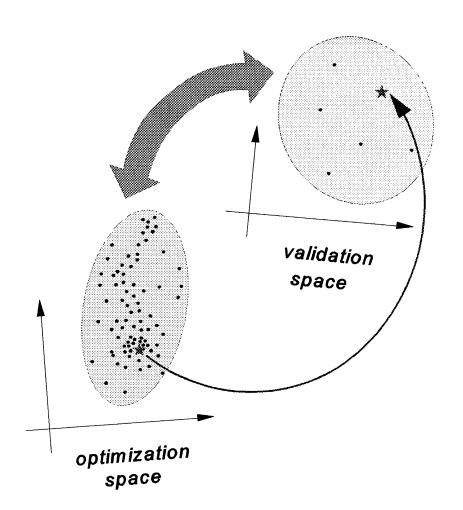

in future, effective utilization of these two types of models will be achieved by the Space Mapping technique

Space Mapping is the key to achieving the accuracy of physical simulation and the speed of circuit-level optimization

# **%**

### **Space Mapping for Future Physical Optimization**

using PBMs for fast optimization using PMs for accurate validation

|  |  | ,<br>Ç |

|--|--|--------|

|  |  | 2      |

|  |  |        |

|  |  |        |

|  |  |        |

|  |  |        |

|  |  |        |

|  |  | Į      |

|  |  |        |

|  |  |        |

|  |  |        |

|  |  |        |

|  |  |        |

|  |  |        |

|  |  |        |

|  |  |        |

|  |  | ъ      |

|  |  | 4      |

|  |  |        |

|  |  |        |

朝